# **SCB100**

# Safety Manual (Original Instructions)

**V0.66**

03/25, 2024

# **Copyright and Disclaimer**

This documentation is the exclusive property of NexCOBOT Co., Ltd. and all information is protected under the intellectual property rights related laws and regulations (including but not limited to copyright law). Any use without authorization is an infringement. No part of this manual may be reproduced, copied, translated or transmitted in any forms or by any means without the prior written permission of NexCOBOT Co., Ltd.

To ensure the correctness and completeness of the document, NexCOBOT reserves the right to change or modify the document at any time without prior notice.

Machinery or equipment in operation is dangerous. Users shall pay special attention and take safety measures before any operation. NexCOBOT shall not be liable for any direct or indirect loss caused by improper use of the product.

#### **NexCOBOT Taiwan Co., Ltd.**

13 F, No. 916, Zhongzheng Rd., Zhonghe Dist., New Taipei City 235015, Taiwan (R.O.C.)

TEL:+886-2-8226-7786

(Website)www.nexcobot.com

(contact)<u>contact@nexcobot.com</u>

# **Revision History**

| Date       | Version | Modifications                                                            |

|------------|---------|--------------------------------------------------------------------------|

| 2024.03.25 | 0.66    | AoU_SCB100_9 is updated.                                                 |

|            |         | Chapter 5.15 is added.                                                   |

|            |         | Modified Figure 3.                                                       |

|            |         | Added DDR4 information in 5.3                                            |

| 2024.03.11 | 0.65    | Modified 1.1 Purpose                                                     |

|            |         | Modified 5.1                                                             |

|            |         | Modified 5.5 Digital Input and 5.6 Digital Output                        |

|            |         | Modified 8 Safety Analysis Results                                       |

|            |         | Modified Appendix B and C.                                               |

| 2023.12.15 | 0.64    | Modified 5.1                                                             |

|            |         | Modified 5.5 and 8.1                                                     |

|            |         | Modified Appendix A and B.                                               |

| 2023.02.07 | 0.63    | Modified DTI description of Table 7.                                     |

|            |         | Modified Table 24 and Table 25 due to new updated FMEDA.                 |

|            |         | Added Note in 5.5.2 for SCB100-IO (Ver.D)                                |

|            |         | Modified 5.5.6 for SCB100-IO (Ver.D)                                     |

| 2022.11.10 | 0.62    | Added Using Digital Inputs with enabling SCB100 test pattern control and |

|            |         | external power description in Ch6.5.3                                    |

|            |         | Modified Table 41                                                        |

|            |         | Modified the specification of vibration and shock                        |

| 2022.11.04 | 0.61    | Added proof test interval description in Ch2.2.                          |

|            |         | Modified the truth table of Table 23.                                    |

|            |         | Modified the start bit from 0 in Table 30.                               |

|            |         | Added specification table in Appendix B.                                 |

| 2022.08.09 | 0.60    | Modified Table 38.                                                       |

|            |         | Added Table 13. Digital inputs hardware response time.                   |

iii

|            |      | Added Table 17. Digital Output hardware response time                          |

|------------|------|--------------------------------------------------------------------------------|

|            |      | Modified Table 41. Other diagnostic related GPIO pin register                  |

|            |      | Modified 5.5.5                                                                 |

|            |      | Added Figure 9. Using Digital Inputs with enabling SCB100 test pattern control |

|            |      | Added 5.5.6                                                                    |

|            |      | Modified Figure 12. Digital output channel test pattern                        |

|            |      | Modified Table 18. Truth Table of digital output channel                       |

|            |      | Modified FMEDA result of Table 24 and Table 25                                 |

| 2021.12.09 | 0.51 | Modified Table 38                                                              |

| 2021.12.02 | 0.50 | Added Ch2, Ch4.4                                                               |

| 2021.11.19 | 0.40 | Added Ch9, Appendix A                                                          |

| 2021.10.29 | 0.30 | Added Ch6, Ch7, Ch8                                                            |

| 2021.10.01 | 0.20 | Added Ch3, Ch4.1,4.2,4.3, Ch5                                                  |

| 2021.09.06 | 0.10 | First draft version of the document (Ch1)                                      |

# Content

| Col | oyright ar | nd Disclaimer                          | ii   |

|-----|------------|----------------------------------------|------|

| Re  | vision His | story                                  | iii  |

| Coı | ntent      |                                        | v    |

| Fig | ure        |                                        | viii |

| Tab | ole        |                                        | x    |

| 1   | Introduc   | ction                                  | 1    |

|     | 1.1.       | Purpose                                | 1    |

|     | 1.2.       | Audience                               | 1    |

|     | 1.3.       | Applied standards                      | 1    |

|     | 1.4.       | Acronyms and Terminology               | 2    |

|     | 1.5.       | Reference Documents                    | 4    |

| 2   | Docume     | ent Scope                              | 6    |

|     | 2.1.       | Prerequisite Documents                 | 6    |

|     | 2.2.       | In Scope                               | 6    |

|     | 2.3.       | Out of Scope                           | 6    |

|     | 2.4.       | SCB100 version                         | 6    |

| 3   | Functio    | nal safety features of SCB100          | 7    |

|     | 3.1.       | Use case and intended application      | 7    |

|     | 3.2.       | Safe function                          | 8    |

|     | 3.3.       | Safe state                             | 8    |

|     | 3.4.       | Mode of operation                      | 8    |

|     | 3.5.       | System response time                   | 8    |

|     | 3.6.       | Safety related parameters              | 9    |

|     | 3.7.       | Requirements to achieve PL d / Cat. 3  | 10   |

| 4   | Safety A   | Architecture                           | 11   |

|     | 4.1.       | SCB100 hardware block diagram          | 11   |

|     | 4.2.       | SCB100 software/firmware block diagram | 12   |

|     | 4.3.       | Operating States                       | 14   |

| 5   | Diagnos   | tic Measures                    | . 16 |

|-----|-----------|---------------------------------|------|

|     | 5.1.      | CPU                             | . 16 |

|     | 5.2.      | Power                           | . 17 |

|     | 5.3.      | DDR4 Memory                     | 20   |

|     | 5.4.      | EMMC                            | . 21 |

|     | 5.5.      | Digital Input                   | . 22 |

|     | 5.6.      | Digital Output                  | 30   |

|     | 5.7.      | NVRAM                           | 35   |

|     | 5.8.      | HW Reset                        | 36   |

|     | 5.9.      | Clock                           | . 37 |

|     | 5.10.     | EtherCAT Slave (Black channel)  | . 38 |

|     | 5.11.     | Ethernet (Black channel)        | . 38 |

|     | 5.12.     | COM port (Black channel)        | . 39 |

|     | 5.13.     | Mini-PCIe (PCIe, Black Channel) | 39   |

|     | 5.14.     | USB2.0 (non-safety related)     | . 39 |

|     | 5.15.     | Safe Logic                      | 40   |

| 6   | Assump    | tion of Use                     | 41   |

| 7   | SCB100    | SW Architecture Recommendations | 44   |

| 8   | Safety A  | nalysis Results                 | 45   |

|     | 8.1.      | FMEDA Report                    | 45   |

|     | 8.2.      | External DDR4 memory            | 46   |

| App | endix A S | SCB100 Specification            | 47   |

| App | endix B S | SCB100 Bring up                 | 49   |

|     | B.1 SCB   | 3100 Package Content            | 49   |

|     | B.2 Inter | nal Connector Definition        | . 52 |

|     | B.3 Pow   | er On SCB100                    | 61   |

| App | endix C I | Hardware & Software interface   | 64   |

|     | C.1 GPI   | O pins                          | 64   |

|     | C.2 Ethe  | ernet                           | 69   |

vi

| C.3 EtherCAT                           | 69 |

|----------------------------------------|----|

| C.4 COM port                           | 69 |

| C.5 Mini-PCle slot                     | 69 |

| C.6 USB                                | 70 |

| Appendix D Environmental and EMC tests | 71 |

| D.1 Environmental tests                | 71 |

| D 2 FMC tests                          | 72 |

# **Figure**

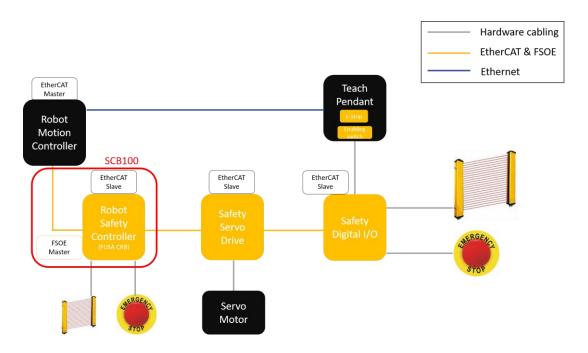

| Figure 1. User scenario of SCB100                                | 7              |

|------------------------------------------------------------------|----------------|

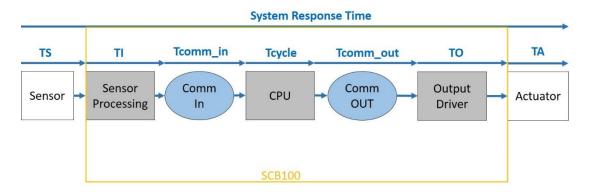

| Figure 2. System Response time of SCB100                         | 8              |

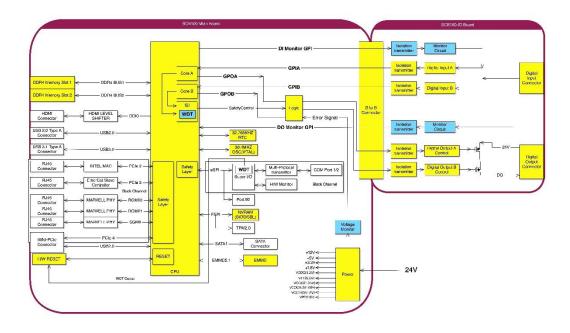

| Figure 3. SCB100 Hardware block diagram                          | 11             |

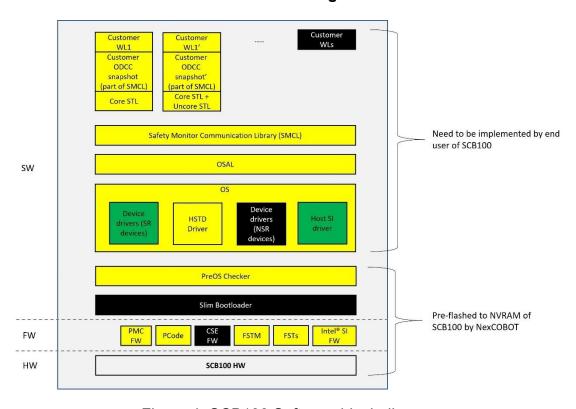

| Figure 4. SCB100 Software block diagram                          | 12             |

| Figure 5. SCB100 State Machine                                   | 14             |

| Figure 6. Digital inputs block diagram                           | 23             |

| Figure 7.Digital input hardware response time waveform           | 27             |

| Figure 8.Digital input channel with test pattern example         | 28             |

| Figure 9. Using Digital Inputs with enabling SCB100 test pattern | n control 29   |

| Figure 10. Using Digital Inputs without enabling SCB100 test pa  |                |

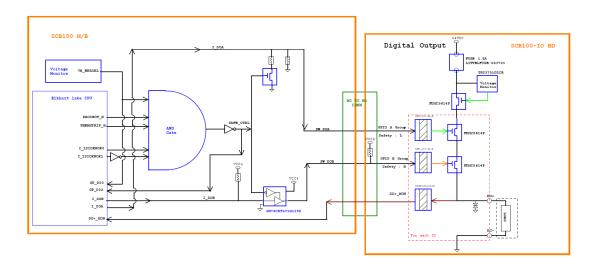

| Figure 11. Digital outputs block diagram                         |                |

| Figure 12. Digital output channel test pattern                   | 34             |

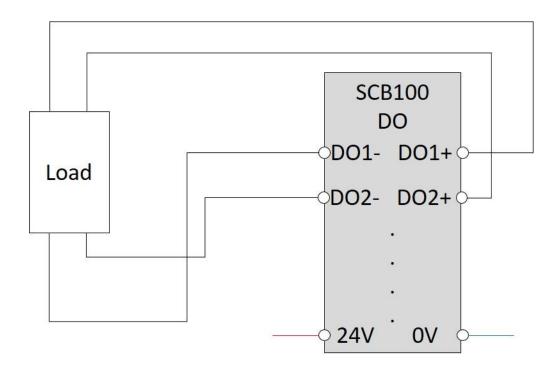

| Figure 13. Connect a load to digital output ports                | 35             |

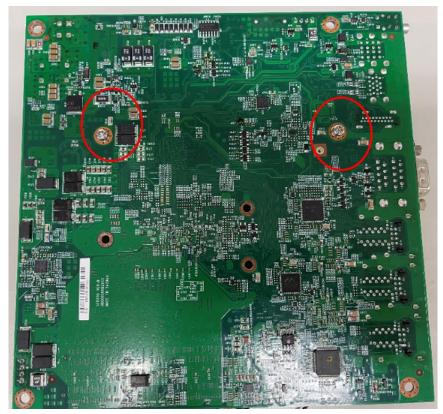

| Figure 14. Copper post long fei                                  | 49             |

| Figure 15. Round head screw W/Spring + flat washer long fei :F   | P3x7L - 1 . 50 |

| Figure 16. Round head screw W/Spring + flat washer long fei :F   | P3x7L - 1 . 50 |

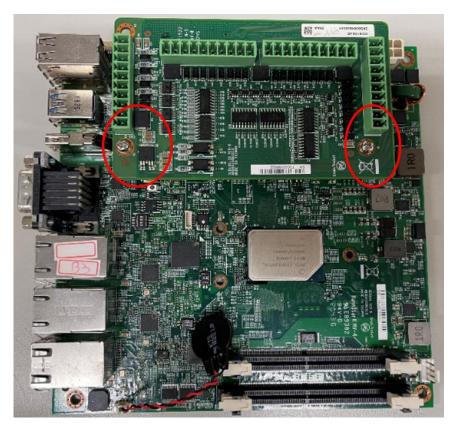

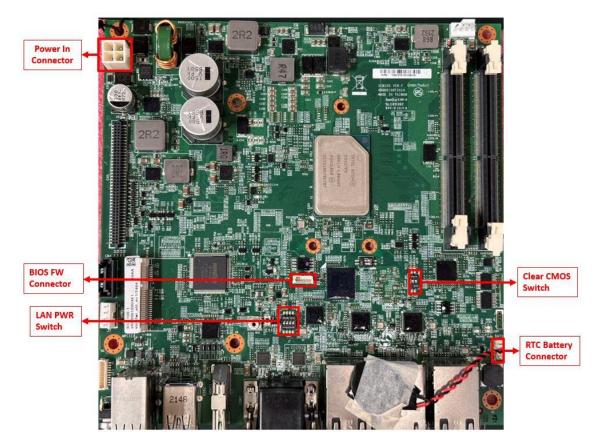

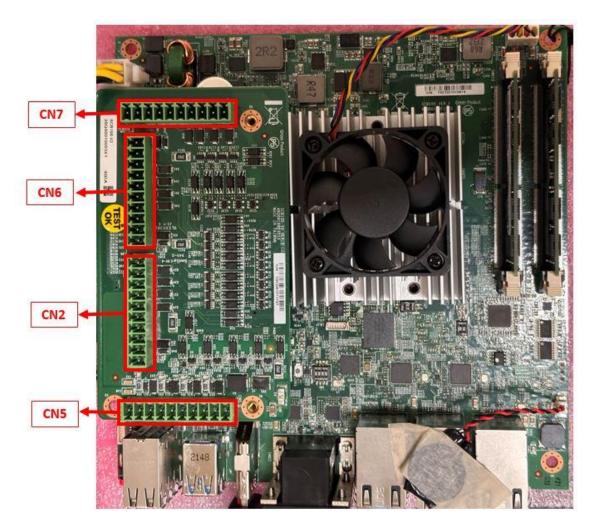

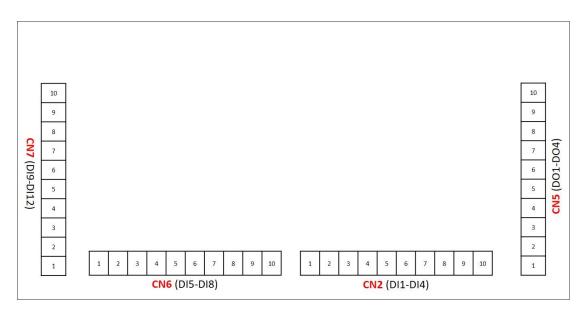

| Figure 17. Internal Connector location                           | 52             |

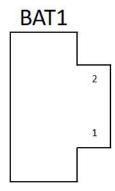

| Figure 18. RTC Battery Connector Port Mapping                    | 52             |

| Figure 19. RTC Battery Sample                                    | 53             |

| Figure 20. Power In Connector Port Mapping                       | 53             |

| Figure 21. Example of DC power-in cable wired to the Power In    | Connector.     |

|                                                                  | 54             |

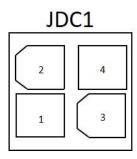

| Figure 22. Clear CMOS Switch Port Mapping                        | 54             |

| Figure 23. LAN PWR Switch Port Mapping                           | 55             |

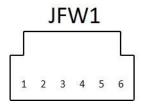

| Figure 24. BIOS FW Connector Port Mapping                        | 56             |

| Figure 25. DIO Connector location                                | 57             |

| Figure 26. DIO Connector in number location                      | 58             |

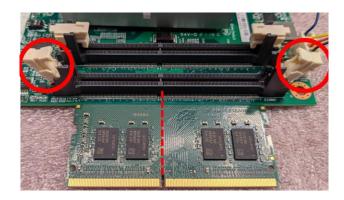

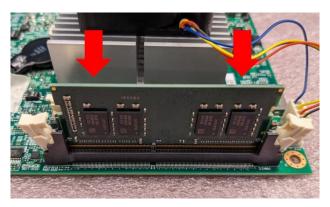

| Figure 27. Install memory card step one                          | 61             |

| Figure 28. Install memory card step two                     | . 62 |

|-------------------------------------------------------------|------|

| Figure 29. Install memory card step three                   | . 62 |

| Figure 30. Install memory card step four                    | . 62 |

| Figure 31. SCB100 Sample Function Top View                  | . 63 |

| Figure 32. Mapping description for GPIO Input Power Monitor | 68   |

# Table

| Table 1. Terminology                                                                 | 2    |

|--------------------------------------------------------------------------------------|------|

| Table 2. Reference Documents                                                         | 4    |

| Table 3. HW elements safety classifications                                          | . 11 |

| Table 4. software/firmware elements safety classifications (Delivery with SCB100 HW) | . 13 |

| Table 5. SW elements safety classifications (Implemented by end user of SCB100)      |      |

| Table 6. SCB100 operating states                                                     | . 15 |

| Table 7. Diagnostic methods of CPU                                                   | . 16 |

| Table 8. Diagnostic method of Power                                                  | . 17 |

| Table 9. Diagnostic methods of Memory                                                | . 20 |

| Table 10. Diagnostic methods of EMMC                                                 | . 21 |

| Table 11. Diagnostic methods of digital inputs                                       | . 24 |

| Table 12. Anti-valent design for DI- channel                                         | . 26 |

| Table 13. Digital inputs hardware response time                                      | . 26 |

| Table 14. Truth table of digital input channel with test pattern                     | . 28 |

| Table 15. Diagnostic methods of digital outputs                                      | . 31 |

| Table 16. Anti-valent design for DO+ channel                                         | . 33 |

| Table 17. Digital Output hardware response time                                      | . 34 |

| Table 18. Truth Table of digital output channel                                      | . 34 |

| Table 19. Diagnostic methods of NVRAM                                                | . 36 |

| Table 20. Diagnostic methods of Clock                                                | . 37 |

| Table 21. AoUs of SCB100                                                             | . 41 |

| Table 22. AoUs on SW Architecture of SCB100                                          | . 44 |

| Table 23. SCB100 FMEDA SIL2 HFT=0 Results                                            | . 45 |

| Table 24. SCB100 FMEDA Cat3 PL=d Results                                             | . 46 |

| Table 25. SCB100 Specification                                                       | . 47 |

| Table 26. Included in SCB100 package                                                 |      |

| Table 27. IS NOT included in SCB100 package                                          | . 51 |

| Table 28. | RTC Battery Connector Pin Definition       | 53 |

|-----------|--------------------------------------------|----|

| Table 29. | Power In Connector Pin Definition          | 53 |

| Table 30. | Clear CMOS Switch Default Setting          | 54 |

| Table 31. | LAN PWR Connector Pin Definition           | 55 |

| Table 32. | LAN PWR Connector Pin Definition           | 56 |

| Table 33. | CN2 (DI1-DI4) Connector Pin Definition     | 58 |

| Table 34. | CN6 (DI5-DI8) Connector Pin Definition     | 58 |

| Table 35. | CN7 (DI9-DI12) Connector Pin Definition    | 59 |

| Table 36. | CN5 (DO1-DO4) Connector Pin Definition     | 59 |

| Table 37. | SCB100 GPIO Pin Status                     | 64 |

| Table 38. | Digital Input related GPIO pin register    | 64 |

| Table 39. | Digital output related GPIO pin register   | 66 |

| Table 40. | Other diagnostic related GPIO pin register | 67 |

| Table 41. | Voltage Monitor Error GPIO pin             | 67 |

| Table 42. | Safety Control Monitor GPIO pin            | 67 |

| Table 43. | GPIO pin Input Power Monitor               | 68 |

| Table 44. | Ethernet HW&SW Interface                   | 69 |

| Table 45. | EtherCAT HW&SW Interface                   | 69 |

| Table 46. | COM port HW&SW Interface                   | 69 |

| Table 47. | Mini-PCIe HW&SW Interface                  | 69 |

| Table 48. | USB HW&SW Interface                        | 70 |

| Table 49. | IEC 61326-3-1 tests                        | 72 |

| Table 50. | IEC 61131-2 tests (EMC related)            | 74 |

| Table 51. | IEC 61000-6-2 / IEC 61000-6-4 tests        | 75 |

#### 1 Introduction

#### 1.1. Purpose

This document is the Safety Manual of NexCOBOT SCB100 written in compliance with EN 61508-2:2010, Annex D and EN 61508-3:2010, Annex D.

The safety controller SCB100 is an EN 61508 Compliant Item including hardware components and software components, which are intended to be integrated into safety-related programmable electronic systems.

SCB100 is leveraging Intel Atom® x6427FE functional safety processor. The user of SCB100 needs to integrate SCB100 with other safety compliant item (e.g. OS, application specific software components) to achieve a complete safety-related programmable electronic systems.

#### NOTE:

All the instructions and constraints as required in this safety manual as well as the manuals as listed in chapter 1.5, must be complied with by the user, in order to achieve the required systematic capability SC 2.

NexCOBOT cannot directly provide the manuals as listed in chapter 1.5 due to NDA concerns, therefore the user of SCB100 is responsible to get these user manuals from the corresponding hardware component / IC venders.

#### 1.2. Audience

The audience for this document is anyone who needs to understand the use of this SCB100 with Intel Atom® x6427FE functional safety processor (Elkhart Lake product) in a functional safety environment. Users include, but are not limited to:

- System integration engineers and architects

- Safety Engineers and Safety Managers

- Engineers integrating and testing the product

- Auditors and Assessors

#### 1.3. Applied standards

EN 61508:2010 Parts 1-7

| EN ISO 13849-1:2023            |

|--------------------------------|

| EN ISO 13849-2:2012            |

| EN IEC 62061:2021              |

| ISO 10218-1:2011, clause 5.4.2 |

| EMC standards                  |

| IEC 61326-3-1:2017             |

| IEC 61131-2:2017               |

| IEC 61000-6-2:2016             |

| IEC 61000-6-4:2018             |

| Environmental standards        |

| IEC 61131-2:2017               |

# 1.4. Acronyms and Terminology

Table 1. Terminology

| Term     | Description                                           |

|----------|-------------------------------------------------------|

| 1001     | Functional safety system architecture as defined in   |

|          | B.3.2.2.1 of EN 61508:6                               |

| AoU      | Assumption of Use                                     |

| BIOS     | Basic Input/Output System                             |

| Cat.3    | Category 3 architecture as defined in EN ISO 13849:1  |

|          | 6.2.6.                                                |

| CCF      | Common Cause failure as defined in EN 61508:4 3.6.10. |

| COM port | Communication port                                    |

| CRC      | Cyclic Redundancy Check                               |

| DC       | Diagnostic Coverage                                   |

| DDR      | Double Data Rate                                      |

| DI       | Digital Input                                         |

| DO       | Digital Output                                        |

| DTI      | Diagnostic Test Interval                              |

| ECC      | Error Correcting Code                                 |

| Elkhart Lake | Formerly Code Name of Intel Atom® x6000E Series Processors |

|--------------|------------------------------------------------------------|

| EMMC         | Embedded Multi Media Card                                  |

| EtherCAT     | Ethernet for Control Automation Technology                 |

| FMEA         | Failure Modes and Effects Analysis                         |

| FMEDA        | Failure Modes Effects and Diagnostic Analysis              |

| FSoE         | FailSafe over EtherCAT                                     |

| FuSa         | Functional Safety                                          |

| FW           | Firmware                                                   |

| HFT          | Hardware Fault Tolerance                                   |

| HW           | Hardware                                                   |

| IBECC        | In Band Error Correcting Code, which is provided by Intel  |

|              | Elkhart Lake SoC                                           |

| IEC          | International Electrotechnical Commission                  |

| ISI          | Intel® Safety Island                                       |

| ISO          | International Organization for Standardization             |

| ITSS         | Interrupt Subsystem                                        |

| MAC          | Media Access Control Address                               |

| NMI          | Non Maskable Interrupt                                     |

| NOK          | Non OK signal derive from Intel Safety Island              |

| NVRAM        | Non-Volatile Random Access Memory                          |

| PMC          | Power Management Controller                                |

| ODCC         | On Demand Cross Comparison                                 |

| OS           | Operating System                                           |

| OSAL         | Operating System Adaptation layer                          |

| OVP          | Over Voltage Protection                                    |

| PHY          | Physical Layer                                             |

| SMCL         | Safety Monitor Communication Library                       |

| SC           | Safety Concept                                             |

| SC3          | Systematic Capability 3 as defined in EN 61508:4 3.5.9.    |

| SIL          | Safety Integrity Level as defined in EN 61508:4 3.5.8      |

| SKU | Stock Keeping Unit                |

|-----|-----------------------------------|

| SRS | Safety Requirements Specification |

| STL | Software Test Libraries           |

| SW  | Software                          |

| UVP | Under Voltage Protection          |

| WL  | Workload (Software application)   |

## 1.5. Reference Documents

Table 2. Reference Documents

| ID   | Document                                                                                | REV   | Document<br>No.           |

|------|-----------------------------------------------------------------------------------------|-------|---------------------------|

| [1]  | Elkhart Lake Safety Manual                                                              | 1.3   | 610115                    |

| [2]  | Elkhart Lake L MCP FMEDA 1001 and Safety<br>Mechanism (Diagnostic) list                 | 1.4   | 615613                    |

| [3]  | Elkhart Lake MCP FMEDA Cat.3, PL=d                                                      | 1.4   | 615614                    |

| [4]  | Elkhart Lake Functional Safety User Guide                                               | 1.0.4 | 610113                    |

| [5]  | 14_SCB100 component level FMEA_2022-<br>04-29_Using_Intel_New_FMEDA_2023_10-<br>02.xlsx | 0.6   | 14                        |

| [6]  | 38_SCB100_Hardware Software Interfaces Specification_V0.2_2023-1101.xlsx                | 0.2   | 38                        |

| [7]  | Super I/O user manual (NCT6122D / NCT6126D Nuvoton Super I/O)                           | 1.4   | NCT6122D<br>/<br>NCT6126D |

| [8]  | PCIe to EtherCAT slave controller user guide                                            | 0.24  | AX99100                   |

|      | (AX99100 PCIe to Multi I/O Controller)                                                  |       | V0.24/06/                 |

|      |                                                                                         |       | 06/16                     |

| [9]  | EtherCAT slave controller user guide                                                    | 1.2   | AX58100                   |

|      | (AX58100 EtherCAT slave controller)                                                     |       | V1.02/11/                 |

|      |                                                                                         |       | 07/18                     |

| [10] | Intel I225 Ethernet controller user guide                                               | 1.92  | 1225                      |

| [ 11 ] | MARVELL PHY user guide | Feb. | MV-      |

|--------|------------------------|------|----------|

|        |                        | 24,  | S107146- |

|        |                        | 2012 | 00       |

## 2 **Document Scope**

#### 2.1. Prerequisite Documents

It is assumed that the reader is familiar with Functional Safety and main functional safety standards, i.e.:

- EN 61508:2010, Parts 1-7

Functional safety of electrical/electronic/programmable electronic safety related systems

- EN ISO 13849-1:2023

Safety of machinery Safety-related parts of control systems

#### Note:

The user of SCB100 must be sufficiently trained by NexCOBOT.

#### 2.2. In Scope

Specifically:

- An overview of the assumed use cases, safety functions and safety requirements

- An overview of the diagnostic measures for which diagnostic coverage is claimed

- Assumption of Use with respect to its intended use

#### 2.3. Out of Scope

Descriptions and guidance on how to use Intel Safety SW libraries (e.g. STL, ODCC) for user own safety SW applications is out of scope of this document. Information on them can be found in [1] and [4].

#### 2.4. SCB100 version

This safety manual is applied the SCB100 version as following.

| Module name       | HW Rev. | SW Rev.                                                                                                             |

|-------------------|---------|---------------------------------------------------------------------------------------------------------------------|

| SCB100 main board | F       | File name: sbl_ifwi_ehl.bin MD5:371bbbe4fe79199337186dfcca7dcaf7 It contains the SW components as listed in Table 4 |

| SCB100 IO board   | D       | -/-                                                                                                                 |

## 3 Functional safety features of SCB100

#### 3.1. Use case and intended application

The general use case of SCB100 is to integrate SCB100 into a safety controller system, where the safety functions of safety controller system are e.g.:

- Receive inputs through hardware-cabling of input devices (e.g. emergency stop button, light curtain, etc.)

- Receive input through safety Ethernet or safety EtherCAT of input devices (e.g. safety servo drive, safety teach pendant, safety digital remote I/O, etc.)

- Process input received from input devices as demanded by safety application software

- Transmit processed data to output devices through hardware-cabling or safety Ethernet

Figure 1. User scenario of SCB100

#### 3.2. Safe function

Safety controller system (where SCB100 is integrated) will perform a logic control receiving inputs, processing them and transmitting outputs in high demand or continuous mode of operation.

Misbehavior of Safety controller system causing wrong, delayed, omitted or committed action (receive input, processing and transmit outputs) including permanent deviation in performance shall be detected and reported.

#### 3.3. Safe state

Safe state is de-energized state.

Demand state is de-energized state.

Normal state is energized state.

#### 3.4. Mode of operation

High demand or continuous mode.

#### 3.5. System response time

Figure 2. System Response time of SCB100

#### Where:

- **TS**: Reaction time required by the selected sensor to react to a process event (device specific, out of scope of SCB100)

- **TI**: The time required by the input module to sample and confirm a sensor event

- Tcomm\_in: Input communication delay. It is equals to the sum of the time to sample a safety input module + the time required to transfer the input value to the CPU

- TCycle: The time which passes between a signal is received by CPU and the output is send from CPU (Including CPU processing safety SW application)

- Tcomm\_out: Output communication delay. It is equals to the sum of the time the time required to transfer the output value from the CPU to the output module + the time to write to a safety output module

- **TO**: The time **TO** for the Safety output module is equal to the time taken by the module to react to input from controller

- TA: Reaction time for the selected actuator (device specific, out of scope of SCB100)

## The System Response Time of Digital input and Digital outputs:

TS: given by the user of SCB100

**TI + Tcomm\_in**: 2 ms (this is a more conservative value, for more precise values please refer to chapter 5.5.3)

**TCycle**: depends on SW application implemented by the user of SCB100

**TO + Tcomm\_out**: 2 ms (this is a more conservative value, for more precise values please refer to chapter 5.6.3)

TA: given by the user of SCB100

#### 3.6. Safety related parameters

| EN 61508 parameters |                                                             |  |

|---------------------|-------------------------------------------------------------|--|

| Туре                | В                                                           |  |

| SIL                 | 2                                                           |  |

| SC                  | 2                                                           |  |

| HFT (1oo1 parts)    | 0                                                           |  |

| HFT (1oo2 parts)    | 1                                                           |  |

| SFF (1oo1 parts)    | >90%                                                        |  |

| SFF (1oo2 parts)    | >60%                                                        |  |

| DTI (1001 parts)    | See Table 7, Table 8, Table 9, Table 10, Table 19, Table 20 |  |

| DTI (1002 parts)    | < 24 hours, See Table 11, Table 15                          |  |

All Rights Reserved.

| PFH                  | 6.103E-08 (at PTI = 20 years / MTTR=MRT=24 hours, 6.1% of SIL2) |

|----------------------|-----------------------------------------------------------------|

| EN ISO 13849-1 parai | neters                                                          |

| PL                   | d                                                               |

| Category             | 3                                                               |

| DCavg                | > 99%                                                           |

| MTTFd                | See Table 25                                                    |

| Mission Time         | < 20 years                                                      |

| PFHd                 | 1.30E-08 (at PTI = 20 years / MTTR=MRT=24 hours)                |

## 3.7. Requirements to achieve PL d / Cat. 3

In order to achieve PL d / Cat. 3, all the requirements as specified in chapter 9 of Intel Elkhart Lake Safety Manual [1] (e.g. dual redundant logical channel, etc.) must be considered by the user of SCB100.

# 4 Safety Architecture

## 4.1. SCB100 hardware block diagram

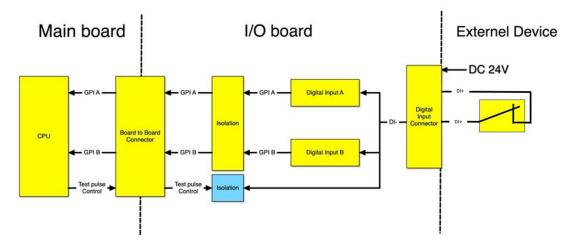

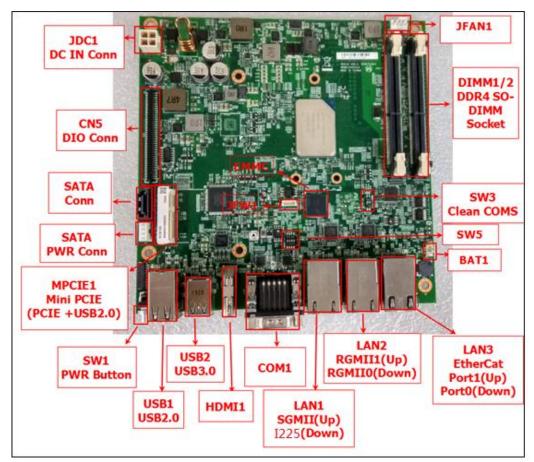

Detailed function block diagram of SCB100 can refer Figure 3.

Figure 3. SCB100 Hardware block diagram

SCB100 has been partitioned in three separate sets of internal elements, with focus on their relevance for functional safety.

In Figure 3, the SCB100 blocks are identified with different colors by using the following protocol:

- Yellow = Safety related

- Yellow with "Safety Layer" = Safety related, Black channel

- White = Not safety related

- Blue = Diagnostic related

Table 3. HW elements safety classifications

| H/W Element Name                 | Safety Classification |

|----------------------------------|-----------------------|

| CPU                              | YES                   |

| POWER                            | YES                   |

| CLOCK(32.768KHZ RTC,38.4MHZ OSC) | YES                   |

| DDR4 MEMORY                  | YES                 |

|------------------------------|---------------------|

| Intel MAC (Ethernet)         | YES (black channel) |

| Marvell PHY (Ethernet)       | YES (black channel) |

| USB2.0                       | NO                  |

| USB3.0                       | NO                  |

| HDMI                         | NO                  |

| Digital inputs               | YES                 |

| Digital outputs              | YES                 |

| EtherCAT                     | YES (black channel) |

| EMMC                         | YES                 |

| COM Port                     | YES (black channel) |

| NVRAM (BIOS/SBL)             | YES                 |

| HW Reset (Include CPU Reset) | Yes                 |

## 4.2. SCB100 software/firmware block diagram

Figure 4. SCB100 Software block diagram

- Yellow = Safety related

- Green = Black channel

#### • Black = Not safety related

The software/firmware elements in Table 4 are pre-flashed into SCB100 NVRAM and are provided with SCB100 HW together to end user. If users need to modified SBL, users need to contact NexCOBOT to request to modify SBL.

Table 4. software/firmware elements safety classifications (Delivery with SCB100 HW)

| software/firmware<br>Element Name | Safety<br>Classification | Note                                                                                                            |

|-----------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------|

| Intel® SI FW                      | YES                      | FSTM (Functional Safety test                                                                                    |

| FSTs                              | YES                      | Manager) and FSTs (Functional Safety                                                                            |

| FSTM                              | YES                      | Tests) are two of major components of Intel SI FW. (Refer to 6.6.2 of [ 1 ]).                                   |

|                                   |                          | Intel SI FW provides measures to detect systematic faults of software components PMC FW and PCode.              |

| Pre-OS Checker                    | YES                      |                                                                                                                 |

| PMC FW                            | YES                      | PMC FW is developed as QM software, its systematic faults are detected by Intel SI FW.                          |

| PCode                             | YES                      | PCode FW is developed as QM software, its systematic faults are detected by Intel SI FW.                        |

| Slimboot loader                   | YES                      | Modified version for SCB100 only                                                                                |

| (SBL)                             |                          | Slim bootloader (SBL) is developed as QM software, its systematic faults are detected by Pre-OS Checker (POSC). |

| CSE FW                            | NO                       |                                                                                                                 |

The SW elements in Table 5 are assumed to be implemented by end user of SCB100, for the detail implementation guidance of these SW elements, please refer to Intel documents which could be found in [1] and [4].

Table 5. SW elements safety classifications (Implemented by end user of SCB100)

| SW Element Name              | Safety<br>Classification | Note                                                                       |

|------------------------------|--------------------------|----------------------------------------------------------------------------|

| OS                           | YES                      | Refer to 3.7.1 of [ 1 ]                                                    |

| Host SI driver               | YES (Black channel)      |                                                                            |

| Device drivers (NSR devices) | NO                       |                                                                            |

| Host STL Driver (HSTD)       | YES                      |                                                                            |

| Device drivers (SR devices)  | YES (Black channel)      |                                                                            |

| OSAL                         | YES                      | Refer to 3.7.6 of [ 1 ]                                                    |

| SMCL                         | YES                      | Refer to 3.7.5 of [ 1 ]                                                    |

| STL                          | YES                      | Refer to 3.7.8 of [ 1 ]                                                    |

| Customer WL                  | YES                      | If the WL is used as a safety application, then this WL is safety related. |

# 4.3. Operating States

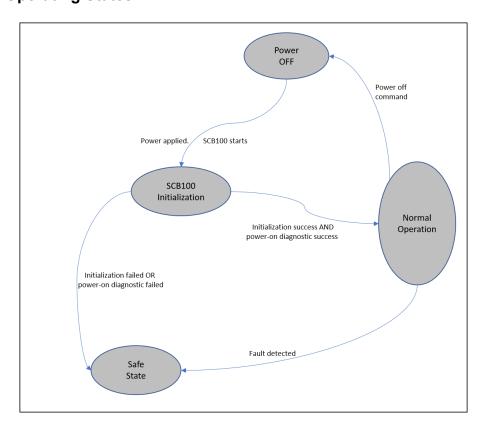

Figure 5. SCB100 State Machine

All Rights Reserved.

Table 6. SCB100 operating states

| State                 | Description                                                                                                                                                                                                                                                                                                                                  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Power off State       | No Power applied to SCB100.                                                                                                                                                                                                                                                                                                                  |  |  |

|                       | All DO output OFF state                                                                                                                                                                                                                                                                                                                      |  |  |

| SCB100 initialization | This state covers initialization of serval components of SCB100, until Elkhart Lake SoC is ready to execute the safety function.                                                                                                                                                                                                             |  |  |

|                       | <ul> <li>Elkhart Lake IP (hardware and firmware) initialization</li> <li>Intel® Slim bootloader and pre-OS checker execution</li> <li>Super I/O initialization</li> <li>PCIe initialization</li> </ul>                                                                                                                                       |  |  |

|                       | <ul> <li>GPIO initialization</li> <li>Memory initialization</li> <li>LAN controller and PHY initialization</li> <li>EtherCAT Salve Controller initialization</li> <li>OS download and initialization</li> <li>Initialization of all software components necessary to support Elkhart Lake functionalities and diagnostic measures</li> </ul> |  |  |

|                       | <ul> <li>Execution and passing of start-up STLs</li> <li>Power on diagnostic (include all functional block e.g. CPU, DI/DO circuit, etc.)</li> <li>All DO output OFF state</li> </ul>                                                                                                                                                        |  |  |

| Normal<br>Operation   | This is the state where the safety application software is being executed.  Output: depends on specific application software                                                                                                                                                                                                                 |  |  |

| Safe state            | When any fault detected, SCB100 will enter safe state. e.g. all DO output OFF state.                                                                                                                                                                                                                                                         |  |  |

# **5 Diagnostic Measures**

#### 5.1. CPU

The Intel Atom® x6427FE CPU supported by SCB100 and is compliant item developed according to EN 61508:2010 targeting a Safety Integrity level up to SIL2.

The Intel Atom® x6427FE CPU supported by SCB100 is also targeted to be compliant with EN ISO 13849 up to Cat. 3, PL d requirements.

Table 7. Diagnostic methods of CPU

| Object | Diagnostics (Normal operation)                                                                                                                                                                                                                                                                                                                                             | DTI / DC                                                                                                                                                                  | Diagnostics (power-on)                                                                                                           | Fault reaction                                                                                                                     |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| CPU    | AoU_SCB100_1  AoU_SCB100_2  The diagnostic measures provided by Intel Atom® x6427FE processor are categorized as:  Hardware:  Measures which are implemented in silicon or MCP package.  Typical measures include parity, ECC, CRC etc. Details provided in section 6.1 in [1].  Software:  Measures which are implemented in FW component or in SW running in Intel Atom® | DTI value is defined by how user implement their software application with Intel STL (refer to section 6 in [1])  (1) SIL2, 1001 DC: 99.48%  (Refer to Ch.10.5.2 in [1].) | According to  CoU_EXT_INT_10 in Table 21 in [_1],  SCB100 provides the power-on diagnostic measures which are listed in Table 8. | When CPU detect faults, ISI of CPU will output safety control (NOK) signal to Logic in Figure 3, and SCB100 will enter safe state. |

| processor cores.        |              |  |

|-------------------------|--------------|--|

| Details are provided in |              |  |

| section 6.4. in [1].    | (2) PLd,     |  |

|                         | Cat.3        |  |

|                         | DCavg:       |  |

|                         | 99.48%       |  |

|                         |              |  |

|                         | (Refer to    |  |

|                         | Ch.10.6.3 in |  |

|                         | [1].)        |  |

#### 5.2. Power

SCB100 power input port shall be powered by the SELV/PELV power supply with a voltage range of [+24VDC-15%, 24VDC+20%] (i.e. 20.4VDC  $\sim$  28.8VDC) to meet IEC 61131-2 standard.

Table 8. Diagnostic method of Power

| Object | Diagnostics (Normal operation)                                                                             | DTI / DC                            | Diagnostics (power-on)              | Fault reaction                                                                             |

|--------|------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------|

| +24V   | UVP and OVP Monitor UVP min range: 19.2V OVP max range: 28.8V (max. withstand voltage: 60V DC)             | - Continuous,<br><2ms<br>- DC = 99% | The same as normal operation.       | When detect power has faults, the Voltage Monitor diagnostic                               |

| 12VSB  | UVP and OVP Monitor OVP monitor : max : 12.6V UVP monitor : min : 11.4V (max. withstand voltage: 28.8V DC) | - Continuous,<br><2ms<br>- DC = 99% | The same<br>as normal<br>operation. | function in  Figure 3 will output Error Signal to Logic, and SCB100 will enter safe state. |

| 5VSB       | UVP and OVP Monitor OVP monitor : max : 5.25V UVP monitor : min : 4.75V (max. withstand voltage: 12V DC)                   | -<br>Continuous,<br><2ms<br>- DC = 99% | The same as normal operation. |  |

|------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------|--|

| 3VSB       | UVP and OVP Monitor OVP monitor : max : 3.46V UVP monitor : min : 3.15V (max. withstand voltage: 12V DC)                   | - Continuous,<br><2ms<br>- DC = 99%    | The same as normal operation. |  |

| 1.8VSB     | UVP and OVP Monitor UVP and OVP Monitor OVP monitor : Max : 1.9V UVP monitor : min : 1.7V (max. withstand voltage: 12V DC) | -<br>Continuous,<br><2ms<br>- DC = 99% | The same as normal operation  |  |

| VPP(2.5V)  | UVP and OVP Monitor OVP monitor : Max : 2.62V UVP monitor : min : 2.38V (max. withstand voltage: 12V DC)                   | -<br>Continuous,<br><2ms<br>- DC = 99% | The same as normal operation  |  |

| VDDQ(1.2V) | UVP and OVP Monitor OVP monitor : Max : 1.26V                                                                              | Continuous,<br><2ms<br>- DC = 99%      | The same as normal operation  |  |

|                | UVP monitor : min : 1.15V                                                                              |                                   |                                    |

|----------------|--------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------|

|                | (max. withstand voltage: 12V DC)                                                                       |                                   |                                    |

|                | UVP and OVP Monitor                                                                                    |                                   |                                    |

|                | OVP monitor : Max : 0.64V                                                                              | Continuous,                       | The same                           |

| VTT(0.6V)      | UVP monitor : min :                                                                                    | <2ms                              | as normal                          |

|                | 0.565V<br>(max. withstand<br>voltage: 12V DC)                                                          | - DC = 99%                        | operation                          |

| VCCIO(1.05V)   | UVP and OVP Monitor OVP monitor : Max : 1.1V UVP monitor : min : 1V (max. withstand voltage: 12V DC)   | Continuous,<br><2ms<br>- DC = 99% | The same<br>as normal<br>operation |

| VCCINAUX(1.8V) | UVP and OVP Monitor OVP monitor : Max : 1.9V UVP monitor : min : 0.7V (max. withstand voltage: 12V DC) | Continuous, <2ms - DC = 99%       | The same<br>as normal<br>operation |

| VCCIN(0.7V-2V) | UVP and OVP Monitor OVP monitor : Max : 2.1V UVP monitor : min : 0.7V (max. withstand voltage: 12V DC) | Continuous, <2ms - DC = 99%       | The same<br>as normal<br>operation |

## 5.3. DDR4 Memory

The SCB100 supports two external DDR4 SO-DIMM memory (Innodisk DDR4 3200 SO-DIMM 16G), maximum memory range can up to 32GB. The function of memory is used for when the user of SCB100 implement their own software applications, memory gives these software applications a place to store and access data on a short-term basis.

Table 9. Diagnostic methods of Memory

| Object          | Diagnostics                                                                                                                                                                                                                                                                                                                                                                 | DTI / DC                                                                                                                                                                                              | Diagnostics | Foult reaction                                                                                                                                                                                                                                                                                                                                     |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Object          | (Normal operation)                                                                                                                                                                                                                                                                                                                                                          | DII/DC                                                                                                                                                                                                | (power-on)  | rault reaction                                                                                                                                                                                                                                                                                                                                     |

| Memory<br>(DDR) | (Normal operation)  AoU SCB100 4 (1) HW IBECC SCB100 protects selected memory regions with IBECC mechanisms detecting two bit faults and correcting single bit faults. Also, IBECC can detect address line fault. (IBECC was provided by Intel Atom® x6427FE Processor, refer to Table 16. in [1], also refer to [3] Tab/Sheet: Safety Mechanisms_Cat3Pld ID: PACKAGE_SMA17 | DTI / DC  - DTI (1) HW IBECC: Continuous, always active diagnostic faults in DRAM are detected by IBECC when the data is used, i.e. when RAM is read  (2) SW ODCC Continuous, safety loop period (the |             | Single bit error When IBECC corrects a single bit error, it generates NMI via ITSS . NMI handler reads IBECC error status registers and report to file system. Every DTI an STL reads the file system and reports a correctable error to ISI. ISI drives ALERT_N and does required correctable error handling tasks.  Double bits error When IBECC |

|                 | (Need to implement by the user of SCB100,  AoU_SCB100_2)                                                                                                                                                                                                                                                                                                                    | period (the<br>user of<br>SCB100<br>parameter)                                                                                                                                                        |             | detects a double bits error (uncorrectable) it generates NMI via ITSS . NMI handler                                                                                                                                                                                                                                                                |

| SW ODCC identifies       | - DC = 99% | reads IBECC error        |

|--------------------------|------------|--------------------------|

| delayed execution,       |            | status registers and     |

| wrong execution,         |            | report to file           |

| stall and wrong          |            | system. An STL           |

| memory                   |            | reads the file           |

| management in Core       |            | system and report        |

| by running safety        |            | uncorrectable error      |

| application in two (or   |            | to ISI. ISI drives       |

| more) independent        |            | NOK (Safety              |

| cores and sending        |            | Control) to Logic        |

| ODCC snapshots to        |            | function of SCB100       |

| ISI. If comparison       |            | in <u>Figure 3</u> , and |

| between the ODCC         |            | SCB100 will enter        |

| snapshots fail, ISI will |            | safe state.              |

| drive "NOK ". (Refer     |            |                          |

| to Table 19. in [1])     |            |                          |

#### 5.4. EMMC

The SCB100 supports one storage device EMMC. EMMC is the hardware component that stores all of digital content, such as documents, pictures, music, videos, programs, application preferences, and operating system represent digital content stored on storage.

Table 10. Diagnostic methods of EMMC

| Object  | Diagnostics (Normal operation) | DTI / DC     | Diagnostics (power-on) | Fault reaction         |

|---------|--------------------------------|--------------|------------------------|------------------------|

|         | AoU_SCB100_5                   | DTI:         | The same               | Since the              |

|         | (1) CRC                        | No DTI as    | as normal              | diagnostics of         |

|         | (Need to implement by          | CRC and      | operation.             | storage was            |

|         | the user of SCB100,            | TIMEOUT are  |                        | implemented by the     |

| Storage | refer to Table 21.             | not periodic |                        | user of SCB100, the    |

| (eMMC)  | conditions of use in           | diagnostic.  |                        | user of SCB100         |

|         | [1], ID:                       | (Faults in   |                        | need to decide what    |

|         | CoU_EXT_INT_04)                | external     |                        | kind of fault reaction |

|         |                                | storage are  |                        | need to do when        |

|         |                                | detected     |                        | detect storage fault.  |

| CRC identifies data     | when the data | l |  |

|-------------------------|---------------|---|--|

| corruption and stall in | is used, i.e. | l |  |

| eMMC by generating      | when eMMC     | İ |  |

| CRC7 for commands       | is read.      | İ |  |

| and CRC16 for data by   |               | 1 |  |

| CRC generators and      | DO - 000/     | 1 |  |

| checks present in       | DC = 99%      | İ |  |

| eMMC controller.        |               | İ |  |

|                         |               | 1 |  |

|                         |               | 1 |  |

| (2) TIMEOUT             |               | l |  |

| (Need to implement by   |               | l |  |

| the user of SCB100,     |               | l |  |

| refer to Table 21.      |               | İ |  |

| conditions of use in    |               | İ |  |

| [ <u>1</u> ], ID:       |               | İ |  |

| CoU_EXT_INT_04)         |               | İ |  |

|                         |               | 1 |  |

| 414:                    |               | İ |  |

| the timeout mechanism   |               | İ |  |

| is implemented to       |               | 1 |  |

| protect memory          |               | 1 |  |

| accesses.               |               | 1 |  |

## 5.5. Digital Input

#### 5.5.1. Function and diagnostic measures

The digital inputs of the SCB100 can detect changes in logic states for each input channel. They are capable of detecting input devices such as normally closed (NC) devices or output signal switching devices (OSSD). If a voltage exceeds or falls below a specific threshold, the SCB100 registers the digital input accordingly. For voltages exceeding 11VDC, the SCB100 detects the digital input as high/1. Conversely, if the voltage drops below 5VDC, the SCB100 identifies the digital input as low/0.

Additionally, each DI channel features a built-in hardware low-pass filter designed to filter out pulse signals shorter than 350µs.

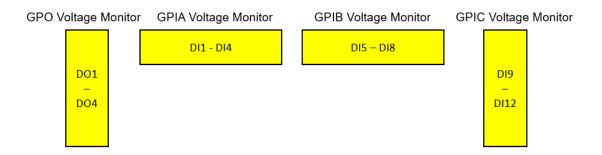

Yellow = Safety related

Blue = Diagnostic related

Figure 6. Digital inputs block diagram

Table 11. Diagnostic methods of digital inputs

| Object           | Diagnostics (Normal operation)                                                                                                                                                                                                       | DTI / DC                                                                  | Diagnostics (power-on)        | Fault reaction                                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | AoU SCB100_6  Digital Input Anti-Valant design  The digital input has an Anti-Valant design, the combination of 2 channel of input signal is listed in Table 12.                                                                     | - DTI Continuous, DTI value is defined by software application - DC = 99% | The same as normal operation. | When the input signal of DIA/DIB is 0/0 or 1/1, indicating a fault in the input, the CPU GPI can read the input signal of DIA/DIB. Users of the SCB100 need to develop their own software application to manage this input fault.                  |

| Digital<br>Input | Over Voltage Protection  The SCB100 contains overvoltage detection chipset that can detect overvoltage on the digital input channels.                                                                                                | - DTI Continuous, <100ms - DC = 99%                                       | The same as normal operation. | When the input voltage exceeds DC 30V, the overvoltage chipset will enter to fault mode with latency 25µs. In fault mode, the overvoltage chipset reduces the input current limitation to 3mA,and the corresponding output channel is deactivated. |

|                  | AoU SCB100 7  Test pattern  Each DI channel has a built-in hardware low-pass filter capable of filtering out pulse signals under 350µs from NC devices or OSSD devices. Users of the SCB100 can enable test pattern function via the | - DTI Continuous, DTI value is defined by software application            | The same as normal operation. | The user of the SCB100 shall execute the test pattern software application on the DI. Upon detecting any fault, the test pattern software                                                                                                          |

| DI Test Pulse Control pin, allowing   | - DC = 99%        |            | shall activate ISI    |

|---------------------------------------|-------------------|------------|-----------------------|

| the system to verify that the DI port |                   |            | NOK to drive the      |

| is still functioning correctly. (See  |                   |            | SCB100 to enter a     |

| 5.5.4)                                |                   |            | safe state            |

|                                       |                   |            | When the +24V         |

|                                       |                   |            | input voltage         |

|                                       |                   |            | exceeds the           |

|                                       |                   |            | overvoltage limit or  |

|                                       |                   |            | falls below the       |

|                                       |                   |            | undervoltage limit,   |

|                                       |                   |            | the "Voltage          |

|                                       |                   |            | Monitor" will cut off |

| Power Input Monitor                   |                   |            | the power output to   |

| The SCB100 is equipped with           | - DTI Continuous, |            | "DI+" to force "DI-"  |

| overvoltage protection (OVP) and      |                   | The same   | low. Consequently,    |

| undervoltage protection (UVP)         | <100ms            | as normal  | the related digital   |

| monitors for the +24V power input.    | <u> </u>          | operation. | input channels will   |

| The voltage limits are set between    |                   | орегацоп.  | enter a safe state.   |

| 28.8V and 20.4V                       | - DC = 99%        |            | Users of SCB100       |

| (max. withstand voltage: 60V DC)      |                   |            | could then            |

|                                       |                   |            | implement their own   |

|                                       |                   |            | software application  |

|                                       |                   |            | to handle this type   |

|                                       |                   |            | of fault by reading   |

|                                       |                   |            | the                   |

|                                       |                   |            | "GPIA/GPIB/GPIC       |

|                                       |                   |            | Voltage Monitor" Pin  |

|                                       |                   |            | (Refer to Table 41).  |

|                                       |                   |            |                       |

Table 12. Anti-valent design for DI- channel

| DI- channel status    | GPIA | GPIB |

|-----------------------|------|------|

| DI- signal is high    | 1    | 0    |

| DI- signal is low     | 0    | 1    |

| DI- channel has fault | 1    | 1    |

| DI- channel has fault | 0    | 0    |

### 5.5.2. Faults and fault exclusion of external wiring

The following fault exclusion measures against wiring faults must be implemented by the user/integrator at application level.

(1) Open circuit of wiring

The safety sensor connected to DI is assumed to use in normally closed mode.

If the circuit of wiring is opened, this situation is failed safe.

(2) Short circuit of power supply, Short circuit to GND, Short circuit to other DI channels

According to ISO 13849-2:2012 Annex D Table D.4:

Short circuits between conductors which are

- permanently connected (fixed) and protected against external damage, e.g. by cable ducting, armouring,

- separate multicore cables,

- within an electrical enclosure (see remark),or individually shielded with earth connection.

#### 5.5.3. Digital Inputs hardware response time

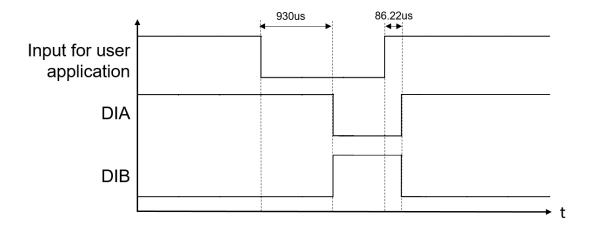

The hardware response time of digital input from 「DI-」 to 「GPIA/B of CPU」 is listed in Table 13.

Table 13. Digital inputs hardware response time

| SCB100-IO: Ver.D 40CA |

|-----------------------|

| Signal transitioning from Low to High | Signal transitioning from High to Low |

|---------------------------------------|---------------------------------------|

| 86.22us                               | 930us                                 |

In Figure 9, when DI receives a low voltage signal from user input, it filters out low voltage signals with a duration less than 930 us. This includes the 350 us from the hardware filter and the response time of the digital input circuit.

Figure 7. Digital input hardware response time waveform

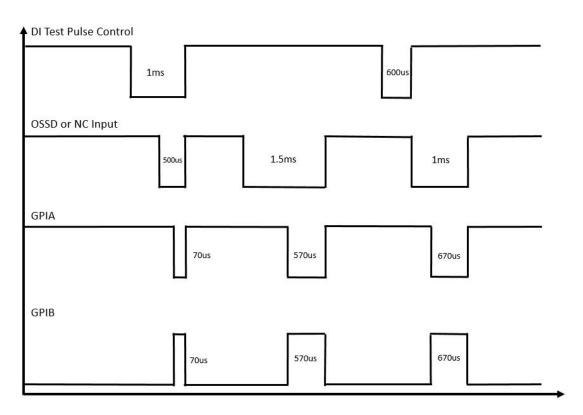

#### 5.5.4. Digital Input channel with test pattern

Figure 8 shows an example of applying a test pattern to a digital input channel. Users of SCB100 shall develop a software application to control the 'Test Pulse Control' GPO (refer to Table 39 for test pulse control) to detect the failure of each digital input channel. Table 14 shows the truth table of digital input channel with test pattern.

Figure 8. Digital input channel with test pattern example

Table 14. Truth table of digital input channel with test pattern

| Signal                | Status | Status        | Status        |

|-----------------------|--------|---------------|---------------|

| DI Monitor Control    | 0      | 1<br>(>350μs) | 0             |

| (OSSD & NC Input) D1- | 1      | 1             | 0<br>(>350μs) |

| GPIA                  | 1      | 0             | 0             |

| GPIB                  | 0      | 1             | 1             |

#### 5.5.5. **Connect** a normally closed (NC) device to the digital inputs

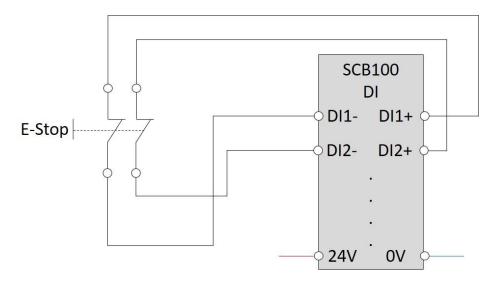

Figure 9 shows the wiring example for connecting SCB100 digital inputs to a safety switch device (e.g., E-Stop button, enabling switch) and enabling test pattern control of SCB100. Users need to use the DI+ channel to output a high voltage to the safety switch device input, and then connect the safety switch device output back to the DI- channel.

Figure 9. Using Digital Inputs with enabling SCB100 test pattern control

#### Note:

For the requirements of fault exclusion measures against wiring faults, refer to chapter 5.5.2.

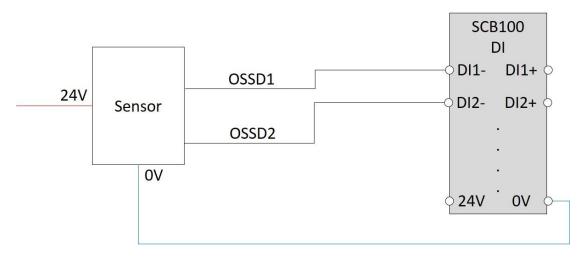

# 5.5.6. Connect an Output Signal Switching Device (OSSD) to the digital input ports

Figure 10 shows the wiring example for connecting SCB100 digital inputs to a safety sensor device with OSSD outputs (e.g., Light curtain). In this scenario, users SHALL NOT use DI+ to provide power to the safety sensor device. Instead, they shall use external 24V power for the safety sensor device.

Figure 10. Using Digital Inputs without enabling SCB100 test pattern control

#### Note:

For the requirements of fault exclusion measures against wiring faults, refer to chapter 5.5.2.

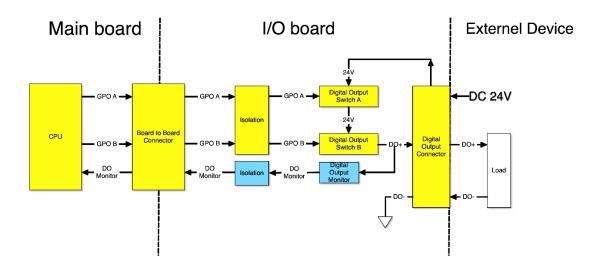

### 5.6. Digital Output

#### 5.6.1. Function and diagnostic measures

Digital Outputs on the SCB100 can generate logic states for each output channel. They enable users to control voltage using their software application. When the software application commands the output to be high, it generates a voltage. Conversely, when the software application commands the output to be low, it is connected to ground and does not produce any voltage. Additionally, digital outputs feature an Anti-Valent design, as demonstrated in Table 16.

Yellow = Safety related

Blue = Diagnostic related

Figure 11. Digital outputs block diagram

Table 15. Diagnostic methods of digital outputs

| Object            | Diagnostics                                                                                                                                                                                                                                                                                                                            | DTI / DC                                                                                | Diagnostics                   | Fault reaction                                                                                                                                                             |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Object            | (Normal operation)                                                                                                                                                                                                                                                                                                                     | DII/DC                                                                                  | (power-on)                    | rault leaction                                                                                                                                                             |

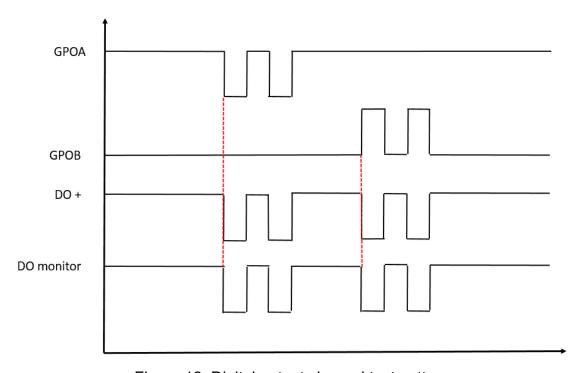

| Digital<br>Output | Test pattern – "Dark  Test"  The user of SCB100 shall implement SW application to diagnose the switch-off capability of each MOFET using the test pattern – "Dark Test" as shown in Figure 12 and Table 18:  If the DO+ output voltage is under 3V, the DO monitor will read back as logic LOW.  If the DO+ output voltage is a little | - DTI  Test pattern Continuous, DTI value is defined by software application - DC = 99% | The same as normal operation. | The user of SCB100 shall execute test pattern SW application to DO. When any fault detected, the test pattern software shall drive ISI NOK to let SCB100 enter safe state. |

| Г                               |             | T          | <u> </u>        |

|---------------------------------|-------------|------------|-----------------|

| higher than 3V, the DO          |             |            |                 |

| monitor will read back          |             |            |                 |

| as logic HIGH,                  |             |            |                 |

| meaning not real                |             |            |                 |

| switched off or de-             |             |            |                 |

| energized.                      |             |            |                 |

|                                 | - DTI       |            | When the +24V   |

|                                 | Output      |            | input voltage   |

| Output over current             | over        |            | exceeds the     |

| protection:                     | current     | The same   | overvoltage     |

| Each DO have an external        | protection: | as normal  | limit, falls    |

|                                 | Continuous, |            | below the       |

| FUSE to protection over current |             | operation. | undervoltage    |

| Current                         | <100ms      |            | limit, or       |

|                                 |             |            | exceeds the     |

|                                 | - DC = 99%  |            | current limit,  |

|                                 |             |            | the "Voltage    |

|                                 |             |            | Monitor" will   |

|                                 |             |            | deactivate the  |

|                                 |             |            | power output to |

|                                 |             |            | "DO+" and the   |

| Power Input monitor:            |             |            | related digital |

|                                 | - DTI       |            | output (DO)     |

| The SCB100 is equipped          | Power       |            | channels will   |

| with overvoltage protection     | Input       |            | enter a safe    |

| (OVP) and undervoltage          | monitor     | The same   | state. Users of |

| protection (UVP) monitors       | Continuous, | as normal  | the SCB100      |

| for the +24V power input.       |             | operation. | can monitor the |

| The voltage limits are set      | <100ms      |            | fault state     |

| between 28.8V and 20.4V         |             |            | through the "   |

| (max. withstand voltage:        | - DC = 99%  |            | GPO Voltage     |

| 60V DC)                         |             |            | Monitor " pin   |

|                                 |             |            | (refer to Table |

|                                 |             |            | 41) and         |

|                                 |             |            | develop their   |